Product Summary

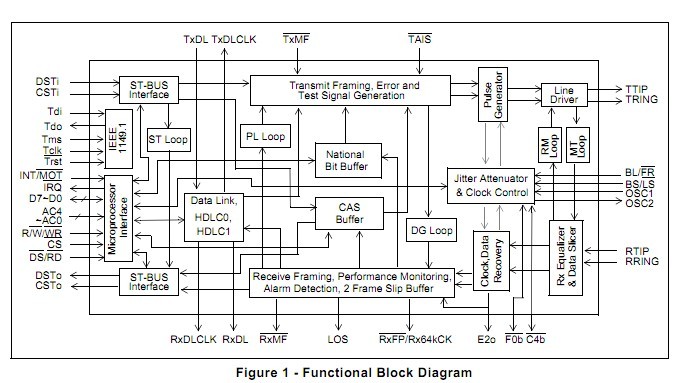

The MT9075BP1 is a single chip device which integrates an advanced PCM 30 framer with a Line Interface Unit (LIU). The framer interfaces to a 2.048 Mbit/s backplane and provides selectable rate data link access with optional HDLC controllers for Sa bits and channel 16. The LIU interfaces the framer functions to the PCM 30 transformer-isolated four wire line. MT9075BP1 applications are: E1 add/drop multiplexers and channel banks, CO and PBX equipment interfaces, Primary Rate ISDN nodes, Digital Cross-connect Systems (DCS).

Parametrics

MT9075BP1 absolute maximum ratings: (1)Supply Voltage, VDD: -0.3 to 7 V; (2)Voltage at Digital Inputs, VI: -0.3 to VDD + 0.3 V; (3)Current at Digital Inputs, II: 30 mA; (4)Voltage at Digital Outputs, VO: -0.3 to VDD + 0.3 V; (5)Current at Digital Outputs, IO: 30 mA; (6)Storage Temperature, TST: -55 to 125 ℃.

Features

MT9075BP1 features: (1)Combined PCM 30 framer, Line Interface Unit (LIU) and link controllers in a 68 pin PLCC or 100 pin MQFP package ; (2)Selectable bit rate data link access with optional Sa bits HDLC controller (HDLC0) and channel 16 HDLC controller; (3)LIU dynamic range of 20 dB; (4)Enhanced performance monitoring and programmable error insertion functions; (5)Low jitter DPLL for clock generation ; (6)Operating under synchronized or free run mode; (7)Two-frame receive elastic buffer with controlled slip direction indication; (8)Selectable transmit or receive jitter attenuator ; (9)Intel or Motorola non-multiplexed parallel microprocessor interface; (10)CRC-4 updating algorithm for intermediate path points of a message-based data link application; (11)ST-BUS/GCI 2.048 Mbit/s backplane bus for both data and signalling.

Diagrams

|

MT900A-UR |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90210 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90210AL |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90220 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90220AL |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90221 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))