Product Summary

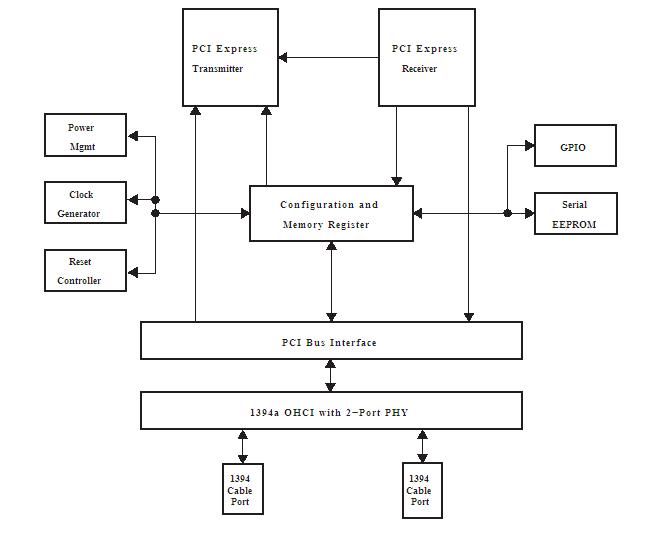

The XIO2200AZGW is a single-function PCI Express to PCI translation bridge where the PCI bus interface is internally connected to a 1394a open host controller link-layer controller with a two-port 1394a PHY. The PCI-Express to PCI translation bridge is fully compatible with the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. Also, the XIO2200AZGW supports the standard PCI-to-PCI bridge programming model. The 1394a OHCI controller function is fully compatible with IEEE Standard 1394a-2000 and the latest 1394 Open Host Controller Interface (OHCI) Specification.

Parametrics

XIO2200AZGW absolute maximum ratings: (1)Supply voltage range: VDD_33: -0.5 V to 3.6 V; VDD_15: -0.5 V to 1.65 V; (2)Input voltage range,VI: PCI Express (RX): -0.6 V to 0.6 V; (3)VI: PCI Express REFCLK (single-ended): -0.5 V to VDD_33 + 0.5 V; VI: PCI Express REFCLK (differential): -0.5 V toVDD_15 + 0.5 V; VI: Miscellaneous 3.3-V IO: -0.5 V to VDD_33 + 0.5 V; VI: 1394a PHY: -0.5 V to VDD_33 + 0.5 V; (4)Output voltage range:VO: PCI Express (TX): -0.5 V to VDD_15 + 0.5V; (5)VO: Miscellaneous 3.3-V IO: -0.5 V to VDD_33 + 0.5 V; (6)VO: 1394a PHY: -0.5 V to VDD_33 + 0.5 V; (7)Input clamp current, (VI < 0 or VI > VDD): ±20 mA; (8)Output clamp current, (VO < 0 or VO > VDD): ±20 mA; (9)Human body model (HBM) ESD performance: 1500 V; (10)Charged device model (CDM) ESD performance: 500 V; (11)Storage temperature range, Tstg: -65℃ to 150℃.

Features

XIO2200AZGW features: (1)Full x1 PCI Express Throughput; (2)Fully Compliant with PCI Express to PCI/PCI-X Bridge Specification, Revision1.0; (3)Fully Compliant with PCI Express Base Specification, Revision 1.0a; (4)Fully Compliant with PCI Local Bus Specification, Revision 2.3; (5)A Second Virtual Channel for Quality-of-Service and Isochronous Applications; (6)Advanced PCI Isochronous Windows forMemory Space Mapping to a Specified Traffic Class; (7)Utilizes 100-MHz Differential PCI Express Common Reference Clock or 125-MHz Single-Ended Reference Clock; (8)Fully Compliant With Provisions of IEEEStd 1394-1995 for a High-Performance Serial Bus and IEEE Std 1394a-2000; (9)Fully Compliant with 1394 Open Host Controller Interface Specification, Revision 1.1; (10)Full IEEE Std 1394a 2000 Support Includes: Connection Debounce, Arbitrated Short Reset, Multispeed Concatenation, Arbitration Acceleration, Fly-by Concatenation, and Port Disable/Suspend/Resume.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XIO2200AZGW |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Exp-PCI Bus Trans Bridge |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

XIO2000A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AEVM |

Texas Instruments |

Interface Modules XIO2000A Eval Mod |

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AGZZ |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express-PCI Bus Translation Bridge |

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AIZHH |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express Bridge Industrial |

Data Sheet |

|

|

||||||||||||

|

XIO2000AIZZZ |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express Bridge Indus ZZZ option |

Data Sheet |

|

|

||||||||||||

|

XIO2000AZHH |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Exp-PCI Bus Trans Bridge |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))